# Supplementing EET Analog Labs with Switched Capacitance Integrated Circuits

William Lehman, Advanced Systems & Materials Asad Yousuf, Savannah State University Muniyappa Venkatesha, Savannah Technical College Chung-Ling Huang, Southern University

#### <u>Abstract</u>

Programmable Analog Integrated Circuits (IC) provides designers the capability to change analog circuits in the field. Although Programmable Switched Capacitance circuits are a technology that deserves study by itself, our main focus here is how such IC's can be used to supplement traditional EET Analog Labs.

Three major players in programmable switched capacitance are Cypress MicroSystems, Anadigm and Lattice Semiconductors. Cypress PSoC is a microcontroller connected to an array of digital and analog switched capacitance blocks. Anadigm produces a Field Programmable Analog Array (FPAA). Anadigm FPAA requires a micro-controller or FPGA to initialize and control the device via a SPI interface. Lattice Semiconductors is a competitor to Anadigm.

Circuits for all three development environments can be designed graphically before the lab to further save time. This paper will report on the utilization of three development environment to supplement the traditional analog labs. Actual circuits examples described were implemented in hardware for Cypress PSoC and Anadigm switched capacitance IC's. The paper will also provide a comparison table to discuss the features of the aforementioned development environments.

### **Introduction**

Using programmable switched capacitance to enhance EET Analog Labs may bring to mind using CPLD/FPGA to enhance EET Digital Labs just a few years ago. The analogy between Digital and Analog Labs is not quite valid. In reality programmable switched capacitance is actually a hybrid digital/analog design technique [12]. As a rule of thumb the clock used to drive the programmable switched capacitance blocks must be about 10 times higher than the frequency of the analog signal to be processed [1][2][3].

There is also similarities that may be found between DSP's and programmable switched capacitance blocks. But once again the analogy between DSP's and programmable switched capacitance blocks is also limited.

Programmable switched capacitance blocks are a subject deserving study in its own right. Which begs the question of how programmable switched capacitance blocks can be used to enhance EET Analog labs.

Of course we perhaps should take a look at what material many EET Analog Labs currently cover. Traditional EET Analog Labs in a nutshell covers circuits where the following discrete components are used [4][5]:

Resistors, Capacitors, Inductors, Diodes, Transistors BJT, FET, MOSFET, OP AMP and Linear Circuits. Typical circuits for EET labs are hard to pin down but often cover: Amplifiers, Filters, Modulation, Oscillator Principles, Rectification, A/D, and D/A.

A great advantage to having students work with discrete components gives the student a tactile learning experience. As we move further into this era of in house PCB software design and in house PCB fabrication capability breadboards and wire warping may well become obsolete [3].

Using programmable switched capacitance to enhance EET Analog Labs in the first phase simply adds switched capacitance experiments that can replace or supplement teaching the following topics[6][7][8]:

- Active Filters

- Amplifiers & Feedback

- Modulation

- A/D and D/A Converters

## **Configuration of Enhanced Analog Labs**

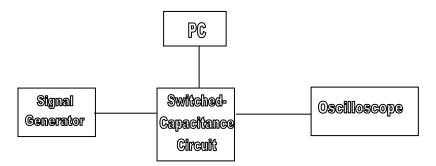

The lab to setup for example filter and gain circuit is the same. There is rather simple signal generator to stimulate the circuit and an Oscilloscope used to ensure the output is as expected. The scope may also be used to confirm the input is as expected. Volt Ohm meters are available for use as well, to give students experience with meters. Figure 1 shows a block diagram of the lab setup.

Figure 1. Block Diagram of Lab Setup

The analysis of the switched capacitance systems that follows is not about there usefulness as designer environments for which the systems were developed. The analysis of the three switched capacitance environments is from the standpoint of how each might be adapted to enhance the EET lab experience vs using more traditional discrete components.

#### <u>Anadigm Designer 2</u>

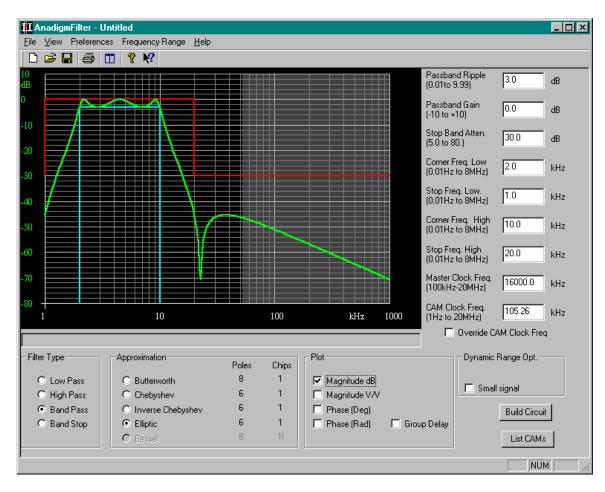

The Anadigm Designer 2 provides a design tool to develop filters. The internal circuit for the IC is automatically generated by depressing the "Build Circuit" button on the filter design tool screen. A example of the filter design tool screen is given in figure 1.0. Some filters require more than one Anadigm IC to implement the circuit.

This feature may or may not be productive from the lab viewpoint in that it eliminates the student from having to design the circuit from scratch. A positive benefit is the capability to try a large number of filters in a lab circuit simple by downloading each one in turn to the actual lab circuit. This is especially useful when the filter is just one section of the lab circuit under consideration.

### Figure 2.0 Filter Design Tool

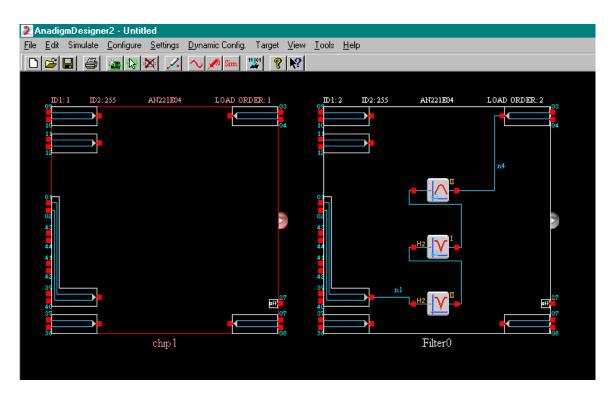

Figure 2.0 shows the generated circuit from the design screen shown in figure 1.0. The students can simulate any filter they design and see the results of a injected signal source by moving around a simulated scope probe.

Figure 3.0 Filter Circuit Generated by Design Software

Circuits can be re-wired or configured by clicking and moving the various components or wires in figure 3.0. The students can also develop their own circuits using the circuit display screen in figure 3.0.

With the exception of filters and PID controllers all circuits are designed and built with screens similar to figure 3.0. Figure 5.0 shows an example of one of the PID controller design screens.

Once again a PID controller can be designed and built using a screen similar to figure 2.0, but the PID controller design tool allows quick design of the circuit.

| Ele View Circuit Help                                                                                                                                      |                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                            |                                                                                                                                                             |

|                                                                                                                                                            |                                                                                                                                                             |

| Design Notes BlockDiagram G(8) TransferFx                                                                                                                  | PLANT                                                                                                                                                       |

| General Properties<br>Target Device Type: AN221E04 Select<br>Controller Type: PID<br>Master Chip Clock<br>Master Chip Clock<br>0 ffset Compensation<br>0 v | PID Constants  Min  Requested  Realized  Max    P:  0  1  1  55    I:  0.000102  1  1  656  1/us    D:  1.02e-005  0.25  0.25  0.8  ms    Signal Path Clock |

| ∬ System<br>For Help, press F1                                                                                                                             | Filter Properties Input                                                                                                                                     |

Figure 4.0 PID Controller Design Screen

Dynamic configuration updates of the Anadigm IC's in real time can create interesting audio applications, which is one area where the programmable IC has an advantage over more traditional analog circuitry.

The Anadigm IC requires a external processor to load the configuration. In an actual design the configuration could be loaded from a processor, PLC, or even memory IC. Anadignm sells a evaluation board that works in conjunction with Anadigm Designer 3.0 software.

Between the simulated scope, design utilities for active filters and PID controllers the students should be able to quickly design and test lab circuit components outside the lab saving valuable time and resources.

## PAC-Designer 3.0

The first step in the PAC-Designer 3.0 environment developed by lattice is to select the type of circuit to download. Using the PAC Library Brower screen shown in Figure 5.0.

| PAC Library Browser                             |                                                                                                                                                                                              | ×                                                    |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Directory: C:\PAC-DESIGNER30\LIBRARY\<br>Files: | <u>I</u> itle:<br><u>S</u> ubject:<br><u>A</u> uthor:<br><u>K</u> eywords:<br><u>C</u> omments:<br>CfgA<br>Type = Elli<br>Fc = 202.3<br>Fs = 284.8<br>PB Ripple<br>SB Atten =<br>Filter ID = | iptical<br>39kHz<br>32kHz<br>= -0.30dB<br>= -47.62dB |

Figure 5.0 PAC Library Brower

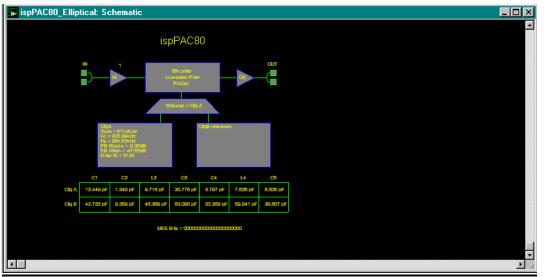

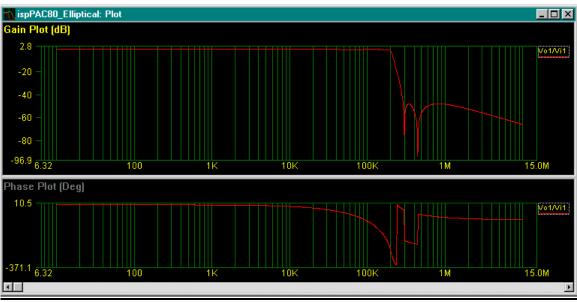

Figure 6.0 shows the downloaded circuit or configuration for a Elliptical filter.

Figure 6.0 Downloaded Elliptical Filter Circuit

The Elliptical filter can be simulated and the results shown on graphs similar to figure 7.0. There are a variety of graphs that may be displayed showing simulated results. Out of the three environments this was the easiest to understand and utilize. The PAC environment seems to allow the least student manipulation of the circuits. The PAC Designer 3.0 environment would seem ideal for labs experiments where students changing filter types would add to the experience for understanding a larger system.

Figure 7.0 Results of Simulation of Elliptical Filters

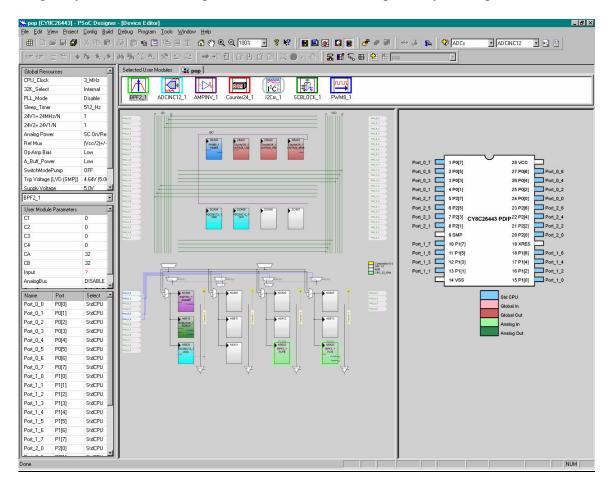

## **PSoC Designer**

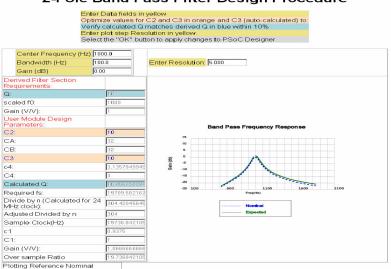

Of the three environments the PSoC designed by Cypress was the most complex to learn but has many uses as far as the lab goes. Like the Anadigm and PAC environments there is a tool to configure different filter types. Figure 8.0 shows one of several screens used in the design of a filter.

2-Pole Band Pass Filter Design Procedure

A disadvantage of the PSoC is the lack of a simulator that the other two switched capacitance environments have.

Since there is a micro-controller that is on the digital bus there is no need for a external processor to load the circuit once the program is download to the IC. The Cypress IC does not require a external crystal to operate the micro-controller the IC can easily be bread boarded (through-hole versions of the IC are available).

There are a large number of digital and analog blocks to work with. Placement of blocks effects how the blocks can be wired or configured internally and externally. Students can design there own blocks since all block parameters are under user control. Different hardware block configurations can be selected under program control. If no programming is desired the students can graphically configure the entire IC and then have code which implements the configuration generated and compiled without the need to program the IC.

The PSoC could double or be used to supplement a course on micro-controllers. The frequency of the switched capacitance blocks is not as high as say Anadigm.

### Figure 9.0 PSoC Configuration Screen

One large advantage is the PSoC support for A/D and D/A circuits. The D/A and A/D circuit blocks can be tied to filters, the input to the A/D is filtered or the output from the D/A is filtered. Examples of using the PSoC to modulate signals is given at the Cypress web site as are expamples of amplifiers with feedback. Numerous other applications are available in the application notes. The students can also take advantage of distance learning audio/visual modules available free at the Cypress web site which should greatly enhance there ability to work through problems on there own.

### **Conclusion**

All three web sites provide good support for their products and have a wealth of information that is useful. Cypress PSoC and Anadigm provide audio/video information to facilitate the leaning curve in using the products.

All three environments may have some efficacy in supplementing existing Analog Laboratory assignments. The table that follows highlights some of the strengths and weaknesses of the three environments.:

| Feature            | Anadigm<br>Designer<br>3.0 | PAC-<br>Designer<br>3.0 | PSoC<br>Designer<br>V4.0 |

|--------------------|----------------------------|-------------------------|--------------------------|

| Simulator          | Yes                        | Yes                     | No                       |

| Micro-Controller   | No                         | No                      | Yes                      |

| Filter Design Tool | No                         | Selected<br>by Block    | Yes                      |

| PID Design Tool    | Yes                        | No                      | No                       |

Time in the lab should be saved by students being able to design and configure filters, amplifiers, modulation circuits, D/A and A/D circuits with filtered inputs. The students can save additional time in the Anadigm and Lattice PAC environments simulating the circuits to ensure they are correct. Circuits or sections of circuits can be simply downloaded from the PC to the actual lab boards saving valuable lab time for building and debugging the circuits with discrete components.

In the case of filters all three environments support high level design tools, many filters may be tried out in a single lab since building the filters with discrete components is not a factor.

#### **References**

1. "Practical Electronics for Inventors" by Paul Scherz McGraw-Hill 2000

2. "Student Manual for the Art of Electronics" by Thomas C. Hayes and Paul Horowitz Harvard, Cambridge University Press 1989

3. "Pros and Cons of replacing discrete logic with programmable logic in introductory digital logic courses" by Kevin Nickels Trinity University ASEE Annual Conference Session 2532

4. "A Proven Different Approach to Teaching Linear Circuits" by Albert J. Rosa and Roland E. Thomas University of Denver/USAF Academy Proceedings of the 2004 American Society for Engineering Education Conference and Exposition.

5. "Know your Lab Styff: Laboratory Proficiency Exam for an Introductory Circuits Class" by Ian M. Nauhaus and Susan M. Lord University of San Diego Proceedings of the 2002 American Society for Engineering Education Annual Conference and Exposition.

6. "Computer Aided Design of Interally Compensated CMOS Operational Amplifiers" b M.G. Guvench University of Southern Main, Gorham, ME 04038 Proceedings of the 2002 American Society for Engineering Education Annual Conference and Exposition.

7. "A Versatile Experiment in Electrical Engineering Technology", Ahmad M. Farhoud, Engineering Technology Department University of Toledo, Proceedings of the 2003 American Society for Engineering Education Annual Conference and Exposition.

8. "Switching and Power Electronics An Innovative Approach", Klaus Wuersig, SUNY College of Technology at Alfred, Session 1547

9. Cypress Semiconductor web site cypressmicro.com

10. Andigm web site andigm.com

11. Lattice web site lattice.com

12. "Design for Reliability of Low-voltage, Switched-capacitor Circuits" by Andrew Masami Abo, A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Engineering-Electrical Engineering and Computer Science in the Graduate Division of the University of California, Berkley Spring 1999.

#### Asad Yousuf

Asad Yousuf is a Professor of Electronics Engineering Technology at Savannah State University. He received his BS in Electrical Engineering from the NED Engineering University, Karachi, Pakistan in 1980 and MS in Electrical Engineering from the University of Cincinnati in 1982 and an Ed.D. from the University of Georgia in 1999. Asad is registered as a Professional Engineer in Georgia, and a Microsoft Certified System Engineer (MCSE).

#### William Lehman

William Lehman received his BS in Electrical Engineering from the Catholic University of America, D.C. in 1979. He has worked through the years testing software and hardware systems in the aerospace and telecommunications industries. He is currently a consultant and may be reached at Advanced Systems & Materials, Lenardtown, Maryland (water@tqci.net).

#### Muniyappa Venkatesha

Muniyappa Venkatesha is a head of the department of Electronics and Computer Engineering Technology at Savannah Technical College. He received his BE degree in Electrical Engineering from BDT college of Engineering Davanagere, Mysore University, India in 1967 and MS in Electrical Engineering from the North Carolina A&T University of Greensboro in 1985 and Ed.S from the Georgia Southern University in 1993.

#### Chun Ling Huang

Chun Ling Huang earned B.S. and M.S. degrees in Mechanical Engineering from Chung Yuan Christian University (CYCU) in Taiwan, and a Ph.D. degree in Mechanical Engineering from the University of Alabama(UA) at Tuscaloosa. Currently, Huang is the Professor of Mechanical Engineering at Southern University, Baton Rouge, Louisiana. He is a member of ASME and ASEE.